存储器设计

|

*************

课程设计报告

课程设计名称:计算机组成原理课程设计课程设计题目:存储器设计

、

院(系):***********

专业:***********

班级:***********

学号:***********

&

姓名:***********

指导教师:***********

完成日期:***********

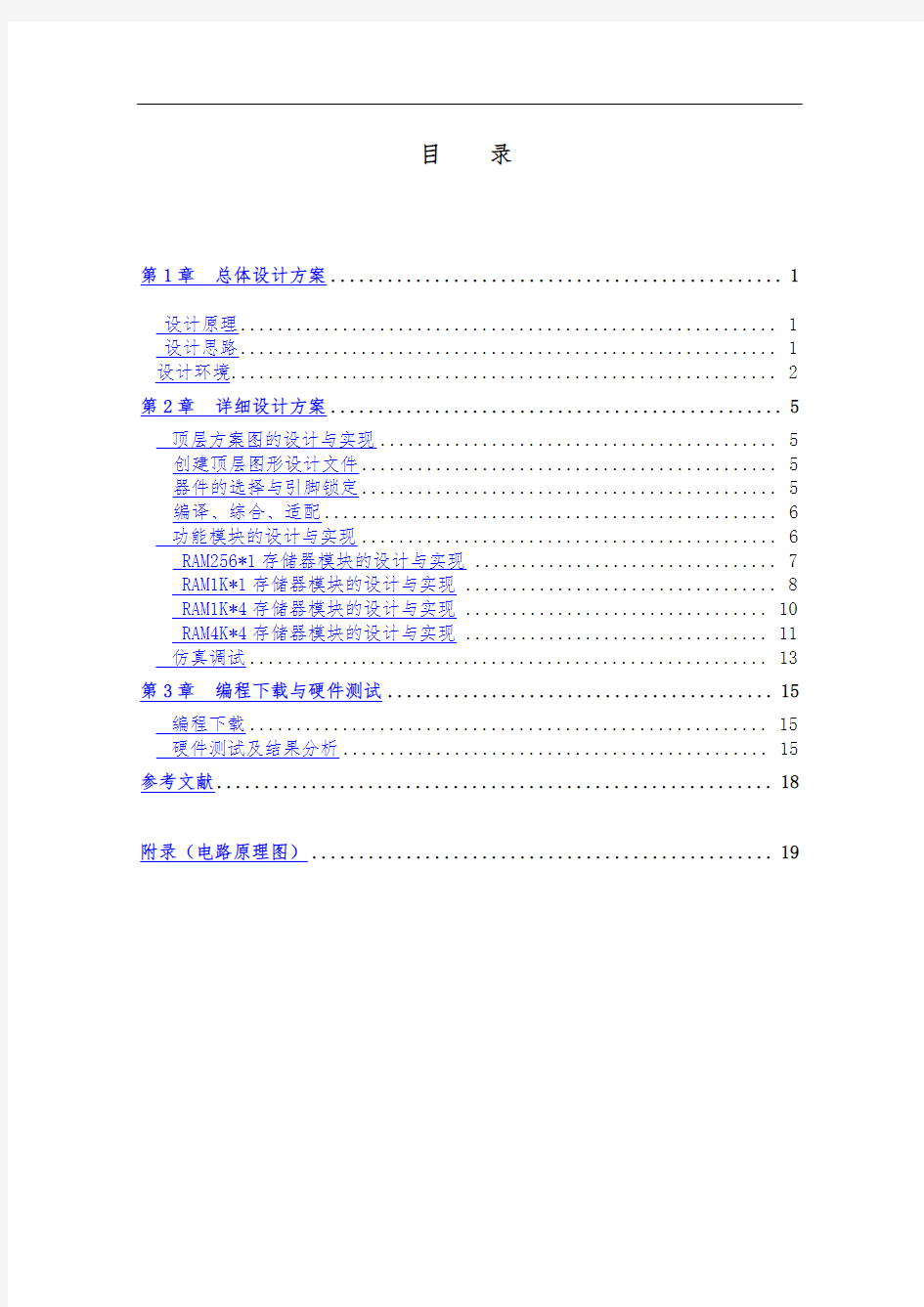

目录

第1章总体设计方案 (1)

设计原理 (1)

设计思路 (1)

设计环境 (2)

第2章详细设计方案 (5)

顶层方案图的设计与实现 (5)

创建顶层图形设计文件 (5)

器件的选择与引脚锁定 (5)

编译、综合、适配 (6)

功能模块的设计与实现 (6)

RAM256*1存储器模块的设计与实现 (7)

RAM1K*1存储器模块的设计与实现 (8)

RAM1K*4存储器模块的设计与实现 (10)

RAM4K*4存储器模块的设计与实现 (11)

仿真调试 (13)

第3章编程下载与硬件测试 (15)

编程下载 (15)

硬件测试及结果分析 (15)

参考文献 (18)

附录(电路原理图) (19)

第1章总体设计方案

设计原理

当一片RAM(或ROM)不能满足存储容量位数(或字数)要求时,需要多片存储芯片进行扩展,形成一个容量更大、字数位数更多的存储器。扩展方法根据需要有位扩展、字扩展和字位同时扩展3种。

(1)位扩展

若一个存储器的字数用一片集成芯片已经够用,而位数不够用,则用“位扩展”方式将多片该型号集成芯片连接成满足要求的存储器。扩展的方法是将多片同型号的存储器芯片的地址线、读/写控制线(W

R)和时钟信号相应连在一起,而将其数据线分别引出接到存储器的数据总线上。

(2)字扩展

若每一片存储器的数据位数够而字线数不够时,则需要采用“字线扩展”的方式将多片该种集成芯片连接成满足要求的存储器。扩展的方法是将各个芯片的数据线、地址线和读写(W

R)控制线分别接在一起,用译码器和时钟信号选择集成芯片。

(3)字、位同时扩展

在很多情况下,要组成的存储器比现有的存储芯片的字数、位数都多,需要字位同时进行扩展。扩展时可以先计算出所需芯片的总数及片内地址线、数据线的条数,再用前面介绍的方法进行扩展,先进行位扩展,再进行字扩展。

设计思路

用1K×4位的RAM集成芯片若干片,构成一个8k×8位的RAM

需要RAM的片数=(8k×8位)/(1k×4位)=16(片)

因为1K×4位的RAM容量1024×8位,表明片内字数1024=210,所以地址线

有10条,即(A

0~A

19

),每字4位,数据线有4条(D

~D

3

)。

而存储容量为8K×8位的RAM,即字数8K=213,所以地址线有13条,即(A

~

A 12),每字8位,数据线有8条(D

~D

7

)。存储器的底层、顶层的设计都采用原理

图设计输入方式,经编译、调试后形成*.bit文件并下载到XCV200可编程逻辑芯片中,经硬件测试验证设计的正确性。存储器的设计框图如图所示。

图存储器的设计框图

设计环境

(1)硬件环境

?伟福COP2000型计算机组成原理实验仪

COP2000计算机组成原理实验系统由实验平台、开关电源、软件三大部分组成实验平台上有寄存器组R0-R3、运算单元、累加器A、暂存器B、直通/左移/右移单元、地址寄存器、程序计数器、堆栈、中断源、输入/输出单元、存储器单元、微地址寄存器、指令寄存器、微程序控制器、组合逻辑控制器、扩展座、总线插孔区、微动开关/指示灯、逻辑笔、脉冲源、20个按键、字符式LCD、RS232口。

COP2000计算机组成原理实验系统各单元部件都以计算机结构模型布局,清晰明了,系统在实验时即使不借助PC 机,也可实时监控数据流状态及正确与否, 实验系统的软硬件对用户的实验设计具有完全的开放特性,系统提供了微程序控制器和组合逻辑控制器两种控制器方式,系统还支持手动方式、联机方式、模拟方式三种工作方式,系统具备完善的寻址方式、指令系统和强大的模拟调试功能。

(2)EDA环境

?Xilinx foundation 设计软件

Xilinx foundation 是Xilinx公司的可编程期间开发工具,该平台(如图所示)功能强大,主要用于百万逻辑门设计。该系统由设计入口工具、设计实现工具、设计验证工具三大部分组成。

设计入口工具包括原理图编辑器、有限状态机编辑器、硬件描述语言(HDL)编辑器、LogiBLOX模块生成器、Xilinx内核生成器等软件。其功能是:接收各种图形或文字的设计输入,并最终生成网络表文件。设计实现工具包括流程引擎、限制编辑器、基片规划器、FPGA编辑器、FPGA写入器等软件。设计实现工具用于将网络表转化为配置比特流,并下载到器件。设计验证工具包括功能和时序仿真器、静态时序分析器等,可用来对设计中的逻辑关系及输出结果进行检验,并详尽分析各个时序限制的满足情况。

图 Xilinx foundation 设计平台

?COP2000集成调试软件

COP2000 集成开发环境是为COP2000 实验仪与PC 机相连进行高层次实验的配套软件,它通过实验仪的串行接口和PC 机的串行接口相连,提供汇编、反汇编、编辑、修改指令、文件传送、调试FPGA 实验等功能,该软件在Windows 下运行。COP2000 集成开发环境界面如图所示。

图 COP2000计算机组成原理集成调试软件

第2章详细设计方案

顶层方案图的设计与实现

顶层方案图实现存储器的输入/输出逻辑功能,采用原理图设计输入方式完成,电路实现基于XCV200可编程逻辑芯片。在完成原理图的功能设计后,把输入/输出信号安排到XCV200指定的引脚上去,实现芯片的引脚锁定。

2.1.1创建顶层图形设计文件

顶层图形文件的设计实体主要由四个RAM4K*4模块组装而成的一个完整的可编程逻辑芯片U39。而以上顶层图形文件的设计可利用Xilinx foundation 中逻辑器件实现,顶层图形文件结构如图所示。

图 8K*8存储器的设计图形文件结构

2.1.2器件的选择与引脚锁定

(1)器件的选择

由于硬件设计环境是基于伟福COP2000型计算机组成原理实验仪和XCV200实验板,故采用的目标芯片为Xilinx XCV200可编程逻辑芯片。

(2)引脚锁定

把顶层图形文件中的输入/输出信号安排到Xilinx XCV200芯片指定的引脚上去,实现芯片的引脚锁定,各信号及Xilinx XCV200芯片引脚对应关系如表所示。

表信号和芯片引脚对应关系

2.1.3编译、综合、适配

利用Xilinx foundation 的原理图编辑器对顶层图形文件进行编译,并最终生成网络表文件,利用设计实现工具经综合、优化、适配,生成可供时序仿真的文件和器件下载编程文件。

功能模块的设计与实现

存储器的底层设计包括RAM256*1存储器模块、RAM1K*1存储器模块、RAM1K*4存储器模块。

2.2.1 RAM256*1存储器模块的设计与实现

该模块由八个RAM32*1存储器、八个与门、一个译码器、一个数据选择器组成。

(1)创建RAM256*1存储器设计原理图。

RAM256*1存储器原理结构如图所示。

图 RAM256*1存储器逻辑框图

(2)创建元件图形符号

为RAM256*1存储器模块创建一个元件图形符号,WE为读写使能信号,D为数据输入信号,WCLK为时钟信号,A0、A1、A2、A3、A4、A5、A6、A7为地址输入信号,O是输出信号。其元件图形符号如图所示。

图 RAM256*1存储器元件图形符号

(3)功能仿真

对创建的RAM256*1存储器模块进行功能仿真,验证其功能的正确性,可用XilinxFoundation 编译器Simulator模块实现。仿真结果如图所示。

图 RAM256*1存储器存储器仿真结果

WE为高电平时,数据输入到地址00011100,并由输出端输出,输入信号为1,输出信号为1,RAM256*1存储器模块的仿真结果正确。

2.2.2 RAM1K*1存储器模块的设计与实现

该模块由模块由四个RAM256*1存储器、四个与门、一个译码器、一个数据选择器组成。

(1)RAM1K*1存储器模块设计原理图。

RAM1K*1存储器模块原理结构如图所示。

图 RAM1K*1存储器模块逻辑框图

(2)创建元件图形符号

为RAM1K*1存储器模块创建一个元件图形符号,WE为读写使能信号,D为数据输入信号,WCLK为时钟信号,A0、A1、A2、A3、A4、A5、A6、A7、A8、A9为地址输入信号,O是输出信号。其元件图形符号如图所示。

图 RAM1K *1存储器元件图形符号

(3)功能仿真

对创建的RAM1K*1存储器模块进行功能仿真,验证其功能的正确性,可用XilinxFoundation 编译器Simulator模块实现。仿真结果如图示。

图 RAM1K*1存储器模块模块仿真结果

WE为高电平时,数据输入到地址00,并由输出端输出,输入信号为1,输出信号为1。RAM1K*1存储器模块的仿真结果正确。

2.2.3 RAM1K*4存储器模块的设计与实现

该模块由模块由四个RAM1K*1存储器组成。

(1)创建RAM1K*4存储器设计原理图。

RAM1K*4存储器原理结构如图示。

图 RAM1K*4存储器逻辑框图

(2)创建元件图形符号

为RAM1K*4存储器模块创建一个元件图形符号,WE为读写使能信号,D0、D1、D2、D3为数据输入信号,WCLK为时钟信号,A0、A1、A2、A3、A4、A5、A6、A7、A8、A9为地址输入信号,O0、O1、O2、O3是输出信号。其元件图形符号如图示。

图 RAM1K*4存储器原件图形符号

(3)功能仿真

对创建的加法器模块进行功能仿真,验证其功能的正确性,可用Xilinx foundation 编译器的Simulator模块实现。仿真结果如图示。

图 RAM1K*4存储器仿真结果

WE为高电平时,数据输入到地址10,并由输出端输出,输入信号为0110,输出信号为0110。RAM1K*1存储器模块的仿真结果正确。

2.2.4 RAM4K*4存储器模块的设计与实现

该模块由模块由四个RAM1K*4存储器、四个与门、一个译码器、四个数据选择器组成。

(1)创建RAM4K*4存储器设计原理图。

RAM4K*4存储器原理结构如图示。

图 RAM4K*4存储器逻辑框图

(2)创建元件图形符号

为RAM4K*4存储器模块创建一个元件图形符号,WE为读写使能信号,D0、D1、D2、D3为数据输入信号,WCLK为时钟信号,A0、A1、A2、A3、A4、A5、A6、A7、A8、A9、A10、A11为地址输入信号,O0、O1、O2、O3是输出信号。其元件图形符号如图示。

图 RAM4K*4存储器原件图形符号

(3)功能仿真

对创建的加法器模块进行功能仿真,验证其功能的正确性,可用Xilinx foundation 编译器的Simulator模块实现。仿真结果如图示。

图 RAM4K*4存储器仿真结果

WE为高电平时,数据输入到地址,并由输出端输出,输入信号为1000,输出信号为1000。RAM4K*1存储器模块的仿真结果正确。

仿真调试

仿真调试主要验证设计电路逻辑功能、时序的正确性,本设计中主要采用功能仿真方法对设计的电路进行仿真。

(1)建立仿真波形文件及仿真信号选择

功能仿真时,首先建立仿真波形文件,选择仿真信号,对选定的输入信号设置参数,选定的仿真信号和设置的参数如表示。

表仿真信号选择和参数设置

输入信号输出信号WE1

A0-Y1200000

O0-O7 D0-D7

(2)功能仿真结果与分析

功能仿真波形结果如图示,仿真数据结果如表示。可以看出功能仿真结果是正确的,进而说明电路设计的正确性。

图功能仿真波形结果

表仿真结果

输入信号输出信号

WE1

A0-A1200000

O0-O7

D0-D7

使能信号WE为高电平时,数据输入到地址00000,并由输出端输出,输入信号为,输出信号为,由此可知结果验证正确,该存储器设计成功。

第3章编程下载与硬件测试编程下载

利用COP2000仿真软件的编程下载功能,将得到*.bit文件下载到XCV200实验板的XCV200可编程逻辑芯片中。

硬件测试及结果分析

利用XCV200实验板进行硬件功能测试。存储器的输入数据通过XCV200实验板的输入开关实现,输出数据通过XCV200实验板的LED指示灯实现,其对应关系如表所示。

表 XCV200实验板信号对应关系

用XCV200实验板的开关控制数据输入,同时观察数码显示管和发光二极管

显示结果,得到如图、、、所示的硬件测试结果。

图硬件测试结果图(1)

WE置1,数据输入到地址0,输入信号为1110,输出信号为1110。

图件测试结果图(2)

WE置1,数据输入到地址0,输入信号为0110,输出信号为0110。

图硬件测试结果图(3)

WE置1,数据输入到地址,输入信号为0010,输出信号为0010。

图硬件测试结果图(4)

WE置1,数据输入到地址,输入信号为0010,输出信号为0010。

输入信号与输出信号相同,说明硬件测试结果是正确的,电路设计完全正确,存储器设计成功。

参考文献

[1] 李景华.可编程程逻辑器件与EDA技术[M].北京:东北大学出版社,2001

[2] 王爱英.计算机组成与结构(第4版)[M].北京:清华大学出版社,2006

[3] 范延滨.微型计算机系统原理、接口与EDA设计技术[M].北京:北京邮电大学

出版社,2006

[4] 莫正坤.计算机组成原理[M].武汉:华中理工大学出版社,1996

[5] 江国强.EAD技术习题与实验[M].北京:电子工业出版社,2005

[6] 百中英.计算机组成原理(第三版)[M].北京:科学出版社,2005

[7] 柳春风.电子设计自动化(EAD)教程[M].北京:北京理工大学大学出版社,2005